### **AFE4114P**

# Ultra Low Capacitance 5-Channel ESD Protection Array

### **General Description**

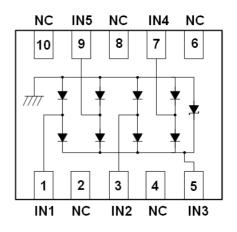

The AFE4114P is a 5-channel ultra low capacitance rail clamp ESD protection diodes array. Each channel consists of a pair of ESD diodes that steer positive or negative ESD current to either the positive or negative rail. A zener diode is integrated in to the array between the positive and negative supply rails.

In the typical applications, the negative rail pin (assigned as GND) is connected with system ground. The Positive ESD current is steered to the ground through an ESD diode and Zener diode and the positive ESD voltage is clamped to the zener voltage. The AFE4114P is idea to protect high speed data lines.

#### **Features**

- 5 channels of ESD protection

- Provides ESD protection to IEC61000-4-2 level 4

- ±17kV air discharge

- ±12kV contact discharge

- Input to GND capacitance: 3.0pF(Max)

- Channel I/O to I/O capacitance: 1.5pF(Max)

- Low clamping voltage

- Low operating voltage (5V)

- Improved zener structure

- Optimized package for easy high speed data lines PCB layout.

### **Application**

- High Definition Multi-Media Interface Protection

- DVI port

- 10 / 100/ 1000M Ethernet interface

- USB2.0 interface

- Flat panel monitors

- Set-top box

- VGA interface.

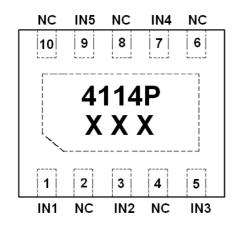

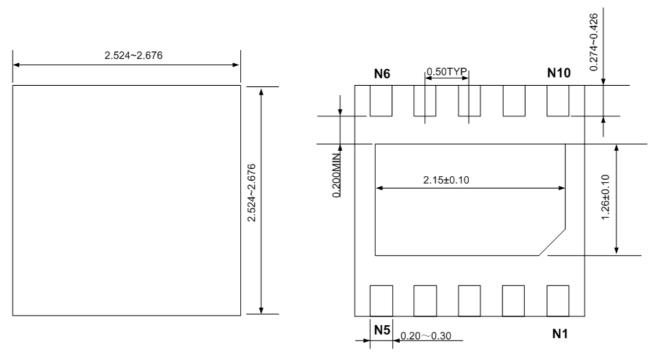

### Pin Description Top View (TQFN-10 ( 2.6X2.6X0.55-0.5 ) )

### **Ordering Information**

| Part Ordering No. | Part Marking | Package                  | Unit        | Quantity |  |

|-------------------|--------------|--------------------------|-------------|----------|--|

| AFE4114PTQFN10RG  | 4114P        | TQFN-10-2.6X2.6X0.55-0.5 | Tape & Reel | 3000 EA  |  |

¾ 4114P Device Code

¾ XXX Date Code

AFE4114PTQFN10RG: 7" Tape & Reel; Pb- Free; Halogen- Free

www.alfa-mos.com

Page 1

# AFE4114P Ultra Low Capacitance 5-Channel ESD Protection Array

### **Absolute Maximum Ratings**

(T<sub>A</sub>=25°C Unless otherwise noted)

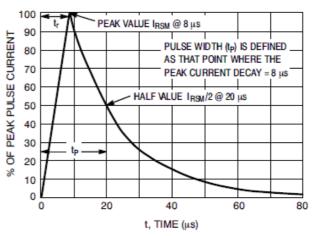

| Parameter                                       | Symbol            | Typical   | Unit                   |

|-------------------------------------------------|-------------------|-----------|------------------------|

| Peak Pulse Power ( t <sub>p</sub> = 8/20 μs )   | P <sub>pk</sub>   | 150       | W                      |

| Peak Pulse Current ( t <sub>p</sub> = 8/20 μs ) | <b>I</b> PP       | 10        | Α                      |

| ESD per IEC 61000 – 4 – 2 (Air )                | V <sub>ESD1</sub> | ±17       | KV                     |

| ESD per IEC 61000 – 4 – 2 (Contact )            | V <sub>ESD2</sub> | ±12       | KV                     |

| Operating Junction Temperature                  | TJ                | -55 ~ 125 | $^{\circ}\!\mathbb{C}$ |

| Storage Temperature Range                       | Тѕтс              | -55 ~ 150 | $^{\circ}\!\mathbb{C}$ |

### **Electrical Characteristics**

(Ta=25°C Unless otherwise noted)

| Parameter                                  | Symbol          | Conditions                                                              | Min. | Тур | Max. | Unit |

|--------------------------------------------|-----------------|-------------------------------------------------------------------------|------|-----|------|------|

| Reverse Working Voltage                    | VRWM            | Any Pin to GND                                                          |      |     | 5    | V    |

| Forward Voltage                            | VF              | IF =10mA                                                                | 0.4  | 0.8 | 1.5  | V    |

| Reverse Breakdown Voltage                  | V <sub>BR</sub> | It = 1mA<br>Any Pin to GND                                              | 6    |     |      | V    |

| Reverse Leakage Current                    | IR              | V <sub>RWM</sub> = 5V , T=25°C<br>Any Pin to GND                        |      |     | 1    | μΑ   |

| Positive Clamping Voltage                  | V <sub>C1</sub> | I <sub>PP</sub> = 1A , tp = 8/20 μs<br>Positive pulse<br>Any Pin to GND |      | 8.5 | 12   | V    |

| Negative Clamping Voltage                  | V <sub>C2</sub> | I <sub>PP</sub> = 1A , tp = 8/20 μs<br>Negative pulse<br>Any Pin to GND |      | 1.8 |      | V    |

| Junction Capacitance<br>Between Channel    | C <sub>j1</sub> | V <sub>R</sub> = 0V , f = 1MHz<br>Between I/O Pin                       |      | 1.3 | 1.5  | pF   |

| Junction Capacitance<br>Between I/O to GND | C <sub>j2</sub> | V <sub>R</sub> = 0V , f = 1MHz<br>Any Pin to GND                        |      |     | 3.0  | pF   |

www.alfa-mos.com

## **AFE4114P**

# Ultra Low Capacitance 5-Channel ESD Protection Array

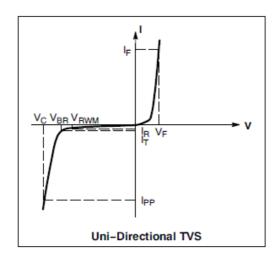

#### **Electrical Parameter**

8 X 20 µs Pulse Waveform

| Symbol           | Parameter                              |  |

|------------------|----------------------------------------|--|

| $I_{pp}$         | Maximum Reverse Peak Pulse Current     |  |

| V <sub>C</sub>   | Clamping Voltage @ IPP                 |  |

| V <sub>RWM</sub> | Working Peak Reverse Voltage           |  |

| $I_R$            | Maximum Reverse Leakage Current @ VRWM |  |

| $I_T$            | Test Current                           |  |

| $V_{BR}$         | Breakdown Voltage @ IT                 |  |

| $I_{F}$          | Forward Current                        |  |

| $V_{\rm F}$      | Forward Voltage @ IF                   |  |

### **Typical Characteristics**

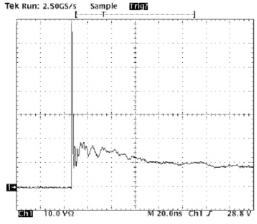

Figure 1 ESD clamping voltage screenshot (Forward 8kv contact IEC 61000-4-2 standard)

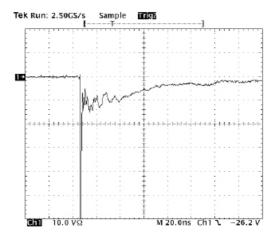

Figure 2 ESD clamping voltage screenshot (Reverse 8kv contact IEC 61000-4-2 standard)

# AFE4114P Ultra Low Capacitance 5-Channel ESD Protection Array

### **Application Information**

### ( Gigabit Ethernet GR-1089 Intra-Building Protection )

These devices are designed to protect low voltage date lines operating at 5.0 volts. When the voltage on the protected line exceeds the reference voltage the steering diodes are forward biased, conducting the transient current away from the sensitive circuitry. Data lines are connected at pins 1, 3, 7 and 9. The center pin should be connected directly to a ground plane. The path length is kept as short as possible to minimize parasitic inductance. Pins 2,4,6,8 and 10 are not connected. Note that pin5 is connected internally to the cathode of the low voltage TVS. It is not recommended that these pins be directly connected to a DC source greater than the breakdown voltage (VB) as the device can latch on as described below.

### ( Gigabit Ethernet ESD Protection )

The TVS employs a complex N-P-P-N structure in contrast to the P-N structure normally found in traditional silicon-avalanche TVS diodes. Since the TVS devices use a 6-layer structure, they exhibit a slightly different IV characteristic curve when compared to conventional devices. During normal operation, the device represents a high-impedance to the circuit up to the device working voltage (VRWM). During an ESD event, the device will begin to conduct and will enter a low impedance state when the punch through voltage is exceeded. Unlike a conventional device, the low voltage TVS will exhibit a slight negative resistance characteristic as it conducts current. This characteristic aids in lowering the clamping voltage of the device, but must be considered in applications where DC voltages are present.

www.alfa-mos.com

## **AFE4114P**

### **Ultra Low Capacitance 5-Channel ESD Protection Array**

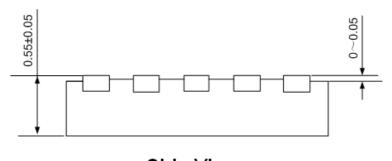

### Package Information ( TQFN-10 ( 2.6X2.6X0.55-0.5 ) )

Top View

**Bottom View**

Side View

©2010 Alfa-MOS Technology Corp. 2F, No.80, Sec.1, Cheng Kung Rd., Nan Kang Dist., Taipei City 115, Taiwan (R.O.C.)

Tel: 886 2) 2651 3928 Fax: 886 2) 2786 8483 ©http://www.alfa-mos.com